## **RESEARCH ARTICLE**

OPEN ACCESS

# Data Encryption and Decryption Algorithm Using Hamming Code and Arithmetic Operations

Kurapati Sundar Teja<sup>1</sup>, Shanmukha Mallikarjuna Bandaru<sup>2</sup>, Kurapati Pavan Teja<sup>3</sup>, Fazal Noorbasha<sup>4</sup>

Department of ECE, K L University, Vaddeswaram, Guntur, AP, India-522502

## ABSTRACT

This paper explains the implementation of data encryption and decryption algorithm using hamming code and arithmetic operations with the help of Verilog HDL. As the days are passing the old algorithms are not remained so strong cryptanalyst are familiar with them. Hamming code is one of forward error correcting code which has got many applications. In this paper hamming code algorithm was discussed and the implementation of it was done with arithmetic operations. For high security some arithmetic operations are added with hamming code process. A 3-bit data will be encrypted as 14-bit and using decryption process again we will receives 3-bit original data. The implemented design was tested on Spartan3A FPGA kit.

Keywords - Encryption, Decryption, Hamming Code, Arithmetic, Verilog HDL, FPGA.

## I. INTRODUCTION

Encryption has long been used by militaries and governments to facilitate secret communication. It is now commonly used in protecting information within many kinds of civilian systems. Encryption is also used to protect data in transit, for example data being transferred via networks (e.g., the Internet, e-Commerce), mobile telephones, wireless microphones, wireless intercom systems, Bluetooth devices and bank automatic teller machines [1].

The encryption standards such as DES (Data Encryption Standard), AES (Advanced Encryption Standard) and EES (Escrowed Encryption Standard) are widely used to solve the problem of communication over an insecure channel [2]. First, the encryption and decryption procedures are much simpler, and consequently, much faster. Second, the security level is higher due to the inherent polyalphabetic nature of the substitution mapping method used here, together with the translation and transposition operations performed in the algorithm [3].

In this paper, the encryption and decryption procedures are explained and the performance is compared with popular encryption algorithms. Recently, a reconfigurable FPGA design is efficient method to implement a digital logic, because FPGA provides a compromise between general-purpose processors and ASIC. The FPGA based design is also more flexible, programmable and can be reprogrammed. FPGA based design can easily be modified by modifying design's software part [4]. Our proposed system is designed in FPGA design style and gate level modeling.

#### II. SYSTEM MODEL AND OPERATION

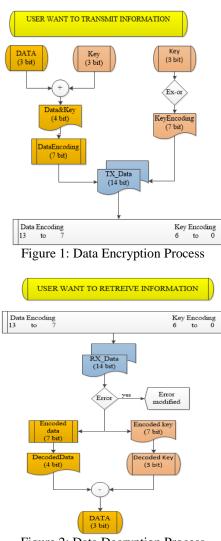

This encryption and decryption process is divided in to two parts. In first part the 3-bit data and key will be converted in to 4-bit data. For this we are using the arithmetic operation addition between 3-bit data and key. 3-bit key will be converted in to 4-bit key by performing ex-or operation between the key bits. In second step the 4-bit addition data and key data will be converted in to 7-bit data using the hamming code process. Finally these two 7-bit data will be clubbed to form a 14-bit data. This final encrypted 14-bit data will be transmitted. In this 14bita 0 to 6 bits are key and 7 to 13 bits are data. Figure 1 shows the encryption process.

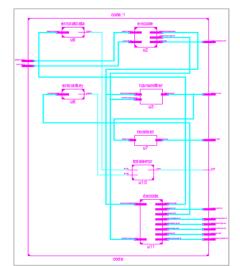

Figure 2 shows the decryption process. This system will receive total 14-bit encrypted data. First it will check the whether the received data is free of error or not. If there is not error in the data then next step will start. In first step total 14-bit data will be divided into two 7-bit data i.e. 7-bit information data and 7-bit key, by using hamming code technique we will get a 4-bit information data and 4-bit key. In second step 4-bit data will subtracted from 4-bit information data. Finally we will get a 3-bit original data. Figure 3 shows the FPGA RTL view.

*Kurapati Sundar Teja et al. Int. Journal of Engineering Research and Applications* www.ijera.com *ISSN: 2248-9622, Vol. 5, Issue 8, (Part - 1) August 2015, pp.81-82*

Figure 2: Data Decryption Process

Figure 3: FPGA RTL View of Data Encryption and Decryption Process System

## III. **RESULTS**

Figure 4 shows the Data Encryption and Decryption Process simulation results of No - error and Figure 5 shows Data Encryption and Decryption Process simulation results – Error. We have tested the results in Spartan3A FPGA kit.

| Nete                                         | Valuet         | Dpe            | 1.5  | 1.1.1      | p00.000 pm                                 |                 | 400 000 pm            |                | 500 800 pe             | 1.1.1.1 | 1000 000 pm    |

|----------------------------------------------|----------------|----------------|------|------------|--------------------------------------------|-----------------|-----------------------|----------------|------------------------|---------|----------------|

| <ul> <li>Outa, in[28]</li> </ul>             | 111            | 1.92           |      | 434        | 006                                        | 310             | 1 140                 | 410            | X 111                  |         | 100            |

| <ul> <li>Market Key, In(2)(2)</li> </ul>     | 811            | C              | 11   |            | 1 1                                        | 11              | 1 330                 | 001            | 1 104                  |         | 111            |

| Encoded_Data(2:0)                            | 1110           | 1101           |      | 11.55      | 0111                                       | 1660            | 1233                  | 1100           | 1 1100                 |         | 1815           |

| <ul> <li>M D. Encrysted Oxfa(150)</li> </ul> | 1110001111111  |                |      |            |                                            |                 |                       |                | 11000011013010         |         | 13063381111111 |

| ICK, Enviryated Data[151]                    | 11100011111111 | 13991991111111 | XIII | 0011111111 | E 0110 3000 1197 LL                        | (81013033139011 | 1 18 100 10 100 1 200 | 00111000011110 | 1 1 100 00 1 10 100 13 |         | 33091091111111 |

| EFFOR                                        |                |                |      |            | 1007 ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( |                 |                       |                |                        |         | 14.000         |

| F M Deceded, Data(30)                        | 1138           | 1 1101         |      | 31,93      | E 0111                                     | 0101            | 10.00                 | 0011           | X 1.839                |         | 101            |

| ChipmarDate(2/)                              | 888            | 1,80           |      | 111        | 1 100                                      | 0.0             | 1 130                 | 410            | X 101                  |         | 110            |

Figure 4: Data Encryption and Decryption Process simulation results – NO Error

| M Data (m[2d]              | 100            | 110               | 111            | 1 155          | 1 10                | LM               | 665              | III                | 110            |

|----------------------------|----------------|-------------------|----------------|----------------|---------------------|------------------|------------------|--------------------|----------------|

|                            |                |                   |                | 190            |                     | 100              |                  |                    |                |

| Markey, in [24]            | 111            | L                 | E              |                | X 661 )             |                  | 001              | A Bh X             | 111            |

| M Encoded_Data(20)         | 1001           | ( 101 )           | 1110           | ( #111         | 0101                | 63160            | ( BHI            | 1100               | 1301           |

| M TK, Enorgated Data(Like) | 10004144155355 | (110011011111111) | 1112001111111  | 01808300180644 | 1110011111111111111 | 0000000000000000 | (00111800811100) | 113000113 00 00 0  | SEDOLADILISESS |

| Rt, Encrypted Data@3kB     | 00000100131111 | (3100110011111)   | 01120000111111 | 11871801100011 | (10110110011)       | 00100100001100   | 011110101110     | 0 10000 100 100 10 | 01001300131111 |

| # ERROR                    | 1              |                   |                |                |                     |                  |                  |                    |                |

| Ceccoled, Data (EK)        | 1999           | 011               | 1110           | FILL           | 0.000               | 6)16             | C HHL            | 1000               | 101            |

| Crigonal-data[2.6]         | 110            | 113               | 111            | 1 193          | 100                 | 110              | X 033            | 111 1              | 133            |

Figure 5: Data Encryption and Decryption Process simulation results – Error

## IV. CONCLUSION

The present data encryption and decryption process is implemented using Verilog HDL with the help of Xilinx ISE Design Suite. The design is verified on Spartan 3A FPGA kit. FPGA increase productivity, reduces cost, and accelerates time to market. The designed system can be used for many applications and also security will be high.

## REFERENCES

- Vinod Shokeen, Niranjan Yadav, "Encryption and Decryption Technique for Message Communication", International Journal of Electronics & Communication Technology, Vol. 2, Issue 2, June 2011, pp. 80-83.

- [2] Obaida Mohammad Awad Al-Hazaimeh, "A New Approach For Complex Encrypting and Decrypting Data", International Journal Of Computer Networks & Communications (IJCNC) Vol.5, No.2, March 2013, pp. 95-103.

- [3] Prakash G L ,Dr. Manish Prateek and Dr. Inder Singh, "Data Encryption and Decryption Algorithms using Key Rotations for Data Security in Cloud System", International Journal Of Engineering And Computer Science, Volume 3 Issue 4 April, 2014 Page No. 5215-5223